本次研讨会的主题一共包括有5个,包括了信号完整性和电源完整性仿真方案信号完整性的并行总线仿真(DDR4)和串行总线仿真(PCIE4.0、PAM4)、电源完整性相关(SSN)以及PCB中过孔(Via)设计专题,各个专题的内容简介如下所示:

专题1:高速数字电路信号完整性和电源完整性解决方案

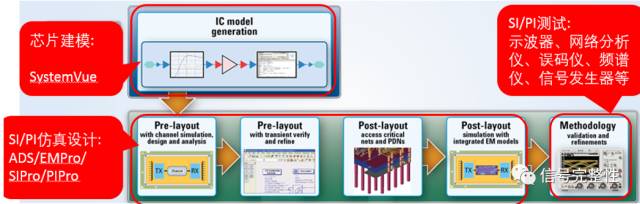

是德科技的 EDA 软件工具提供了针对高速数字电路信号与电源完整性的完整解决方案。在这一专题中,将为大家详细介绍这一解决方案,包括:数字芯片的 IBIS AMI 建模,高速链路从系统从版图前仿真到后仿真的完整仿真流程,针对三维结构的全波电磁场仿真器,与测试测量仪表的交互验证。

专题2:揭秘高速 PCB 设计中的过孔设计技巧

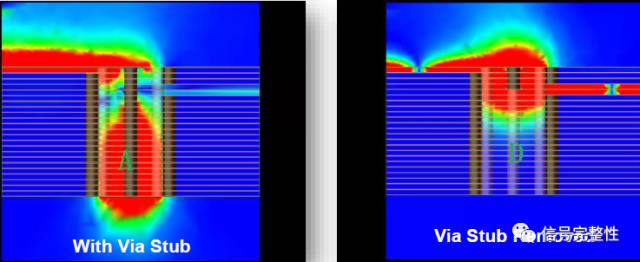

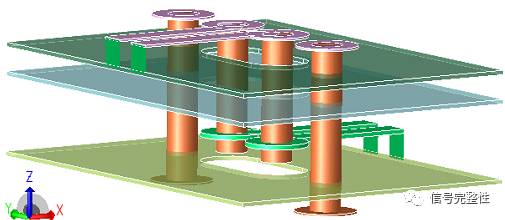

通过板层垂直传播的高速信号比沿相同层水平传播的信号要复杂几倍,设计难度较大。本专题介绍过孔构建的基础知识及其对高速信号的影响。我们将重点介绍更好的过孔设计技巧,并介绍不同的仿真技术,以产生更好的的互连效果,并允许您进行各种方案的折衷考虑。我们还将介绍 ADS2017 中最新的过孔设计工具 Via Designer 是如何快速高效地实现过孔的设计。

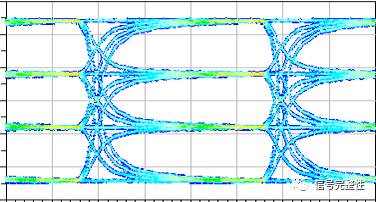

专题3:PAM-4 仿真与设计

摘要:两大标准组织 OIF 和 IEEE 都考虑在下一代的网络传输中采用 PAM-4 的信号传输技术。虽然 PAM-4 能解决高速速率下信号的传输效率问题,但是 PAM-4 的对信号的噪声更加的敏感,使得在工程师在设计、仿真和测试中也会遇到很多新的问题。在这部分中将主要讨论 PAM-4 的仿真和设计相关的内容。

专题4:使用 SSN 引起的抖动模型进行基于统计方法的 DDR4 裕度精确估计

统计方法在设计系统中已经普遍使用,极低的 BER 需要随机抖动的准确预测,DDR4 就是一个示例。这种方法的局限性是,不能对由于 SSO / SSN 引起的电压噪声建模,因为统计方法中假定系统是时不变系统。在 Designcon2017 大会上,Keysight 提出了一种解决方案,从瞬态仿真计算得出的电压噪声中提取抖动模型,然后在统计分析中使用该模型来精确预测时序和电压裕度。文中提供了测量数据以验证该方法。

专题5:配备中继器的 PCIe Gen4 端到端系统级仿真

高速串行链路设计方案空间随着数据速率的增加、信道拓扑的多样化以及有源组件的调整参数增加而变得越来越复杂。PCI-Express Gen-4 就是一个特别典型的应用示例,其设计方案空间是一个需要解决的棘手问题。本文旨在通过提供一个包括定义、执行和分析系统级仿真(包括 PCIe4 Root Complex、中继器和端点)的操作指南,帮助系统工程师了解这些设计挑战。

我们将在成都、武汉和南京分别举办。具体时间和地点如下:

时间地点

成都站

时间:2017年12月19日

地点:成都天府丽都喜来登酒店四楼嘉陵岷江厅

地址:成都市青羊区人民中路一段15号

武汉站

时间:2017年12月21日

地点:武汉光谷皇家格雷斯大酒店 一楼福恩殿

地址:武汉市东湖高新技术开发区大学园路2号

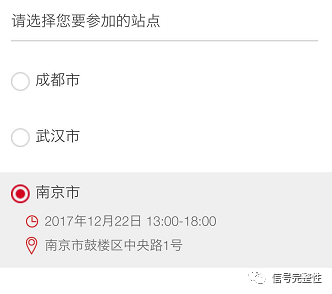

南京站

时间:2017年12月22日

地点:南京绿地洲际酒店6楼钟山3厅

地址:南京市鼓楼区中央路1号

虽然是三个不同的城市,报名渠道是相同的,所以请各位工程师小伙伴报名的时候一定要选择好参加的城市,如下所示:

快速注册通道

报名即可参与现场抽奖,100%中奖。

如果您和您的、同事/小伙伴/最好的工作搭档,双双注册了北京IC测试研讨会,并双双来到现场,请出示您的英雄帖,您将获得一份属于你们两个人的共同的小礼物。

具体的活动日程如下所示:

活动日程

| 时间 | 主题演讲 |

|---|---|

13:00 - 13:10 | 是德科技 EEsof EDA 软件简介 |

13:10 - 13:40 | 高速数字电路信号完整性和电源完整性解决方案 |

13:40 - 14:20 | 揭秘高速 PCB 设计中的过孔设计技巧 |

14:20 - 15:00 | PAM4 仿真与设计 |

15:00 - 15:30 | Tea Break |

15:30 - 16:10 | 使用 SSN 引起的抖动模型进行基于统计方法的 DDR4 裕度精确估计 |

16:10 - 16:50 | 配备中继器的 PCIe Gen4 端到端系统级仿真 |

16:50 - 17:00 | 抽奖 |

报名即可参与现场抽奖